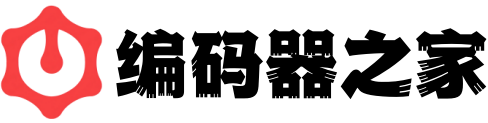

Los encóderes absolutos pueden comunicarse con el controlador mediante comunicación serie o paralela, bus de campo o protocolos basados en Ethernet como EtherCAT. De estas opciones de interfaz, la comunicación serie es una solución más sencilla que la comunicación paralela (que requiere un par de hilos trenzados para cada salida) y es muy adecuada para aplicaciones que no son tan complejas como para requerir protocolos basados en bus de campo o Ethernet. Aquí veremos cuatro de las corrientes más comunesEncoder absolutoDiferencias entre las interfaces serie: SSI, BiSS, Hiperface DSL y EnDat 2.2.

SSI: Interfaz serie síncrona

Como su nombre indica, SSI es un protocolo de sincronización, lo que significa que los datos se transmiten de forma sincrónica desde el encóder al controlador mediante señales de reloj o pulsos suministrados por el controlador. La salida del encóder puede ser binaria o en código Gray, con 1 bit transmitido por impulso de reloj, y una longitud de palabra estándar de 13 bits para encóderes monovuelta y 25 bits para encóderes multivuelta.

Fig.1 La interfaz del codificador SSI es sencilla, con sólo cuatro hilos para la comunicación (par trenzado para los datos y par trenzado para las señales de reloj) y dos hilos para la alimentación.

Según la norma RS-422, la interfaz serie síncrona se comunica mediante dos pares de hilos de par trenzado: un par para la señal de datos diferencial y otro para la señal de reloj diferencial. Otros dos hilos se utilizan para alimentar el codificador. La frecuencia de reloj o la velocidad de transmisión de datos puede ser de hasta 1,5 MHz; la frecuencia exacta real depende de la longitud del cable. Para garantizar la integridad de los datos, algunos codificadores SSI admiten transmisiones múltiples (también conocidas como transmisiones "multitrayecto" o "desplazamiento circular"), en las que los mismos datos se transmiten varias veces y el controlador compara los datos transmitidos para asegurarse de que coinciden.

Biss: Interfaz serie síncrona bidireccional

La interfaz serie síncrona bidireccional es un protocolo abierto, similar a SSI, en el que la transferencia de datos se sincroniza mediante una señal de reloj del controlador, utilizando el protocolo Biss con velocidades de reloj de hasta 10 MHz.Biss sigue utilizando dos pares de hilos trenzados: un par para la señal de datos diferencial y otro par para la señal de reloj diferencial. Además, se añaden dos hilos más para la fuente de alimentación.

A diferencia de SSI, que sólo admite comunicación unidireccional, Biss admite comunicación bidireccional, lo que significa que el controlador puede leer y escribir en la memoria no volátil del codificador, donde los registros contienen la información de identificación del codificador.El codificador Biss también puede enviar datos, como la temperatura, al controlador según sea necesario. Otra característica exclusiva de Biss en comparación con SSI es que el host determina y compensa cualquier retraso en la transmisión durante cada ciclo de datos, lo que permite velocidades de transmisión de hasta 10 Mbps.

La última versión de BiSS es BiSS-C (C = Continuly), que a menudo se denomina simplemente "BiSS".

Fig.2 BiSS permite la comunicación bidireccional, por lo que se utilizan dos cables para comunicarse con el controlador (MA+ y MA-), y dos cables para comunicarse con el codificador (SL+ y SL-), además de dos cables de alimentación.

A diferencia de los codificadores SSI, los codificadores Biss pueden conectarse punto a punto o a través de un bus. Cuando se conectan a través de un bus, los datos de todos los codificadores se sincronizan con el maestro en una trama continua, en lugar de transmitirse individualmente. Biss también utiliza comprobaciones de redundancia cíclica (CRC) para la comprobación de errores, un método más fiable que las transmisiones múltiples. También existe una interfaz de seguridad Biss para aplicaciones de seguridad según la norma IEC 61508 SIL 3.

Hiperfaz DSL

Hiperface DSL, HIgh PERformance InterFACE Digital Servo Link, era originalmente una interfaz patentada desarrollada por SICK. Sin embargo, en 2016, SICK "abrió" la interfaz a través de un modelo de licencia, permitiendo a otros fabricantes integrar la tecnología en sus productos.

A diferencia de su predecesor Hiperface, Hiperface DSL es un protocolo totalmente digital que utiliza sólo dos hilos para la comunicación bidireccional y la alimentación del codificador, agrupados con los hilos de alimentación del motor (aunque se requiere un transformador para mejorar el rechazo del ruido en modo común). Esto tiene la ventaja de eliminar la necesidad de una conexión de codificador independiente entre el motor y el controlador.Hyperfaces DSL es compatible con RS-485 y tiene una velocidad de transmisión de datos de 9,375 Mbaud.Los datos pueden transmitirse cíclicamente (lo más rápido posible) o sincronizarse con el reloj del controlador.

Fig.3 La Hiperface DSL incluye canales para realimentación de posición, intercambio de parámetros, datos de proceso, posición segura y datos de monitorización de estado (SensorHub), todos ellos transmitidos a través de dos hilos (que pueden integrarse en el cable del motor).

La arquitectura Hiperface DSL también incluye canales para la transmisión de datos de parámetros del motor, datos de monitorización de estado y movimientos de seguridad integrados, transmitiéndose los datos a través de dos líneas de comunicación digital. Esta redundancia y comprobación de errores permite que la interfaz Hiperface DSL cumpla la norma de seguridad SIL3.

EnDat 2.2

La interfaz de datos de encoder o EnDat 2.2 de HEIDENHAIN es un estándar bidireccional sincronizado que utiliza cuatro líneas para la comunicación: dos líneas para datos diferenciales y dos líneas para señales de reloj diferenciales. Además de dos hilos para la fuente de alimentación y dos hilos para la batería tampón o la fuente de alimentación paralela, EnDat 2.2 puede proporcionar frecuencias de reloj de hasta 2 MHz y, en algunos modelos, la compensación adicional de los retardos de propagación hace posibles frecuencias de hasta 16 MHz.

Desde que Hiperface DSL se ha convertido en una interfaz "abierta", EnDat es la única que sigue siendo propietaria.Encoder absolutointerfaz serie (cabe señalar que el protocolo Hiperface original también sigue siendo propietario).

FIG.4 Con compensación de retardo transmitido, EnDat 2.2 puede proporcionar frecuencias de reloj de hasta 16 MHz.

EnDat 2.2. también puede leer, escribir o actualizar información almacenada en el encóder y puede transmitir datos (por ejemplo, información del sensor o información de diagnóstico) del encóder al controlador. El tipo de datos transferidos (por ejemplo, posición absoluta, información de diagnóstico o parámetros) se envía desde el controlador al encóder mediante comandos de modo. Al igual que Biss e Hiperface DSL, EnDat 2.2 cumple la norma de seguridad SIL3.

原文链接:https://www.bmq123.com/es/58.html